Verilog | Sublime Text 中 Verilog Gadget插件说明

迪丽瓦拉

2025-05-29 06:53:29

0次

文章目录

- 一、Verilog Gadget

- 1. Generate Testbench 生成测试平台

- 2. lnsert Header 生成顶部注释文档

- 3. lnsert Snippet 插入片段 (ctrl+alt+p)

- 4. Instantiate Module 实例化模块

- 5. Simulation Template 仿真模板

- 6. Repeat Code with Numbers 用数字重复代码(ctrl+f12)

- 7. 代码自动对齐

- 总结

一、Verilog Gadget

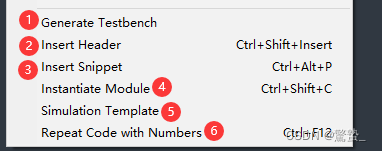

右键菜单如下:

1. Generate Testbench 生成测试平台

- 包括模块的实例和信号

- 测试平台被创建为一个systemverilog文件。

2. lnsert Header 生成顶部注释文档

默认内容如下:

// This is a simple example.

// You can make a your own header file and set its path to settings.

// (Preferences > Package Settings > Verilog Gadget > Settings - User)

//

// "header": "Packages/Verilog Gadget/template/verilog_header.v"

//

// -----------------------------------------------------------------------------

// Copyright (c) 2014-{YEAR} All rights reserved

// -----------------------------------------------------------------------------

// Author : yongchan jeon (Kris) poucotm@gmail.com

// File : {FILE}

// Create : {DATE} {TIME}

// Revise : {RDATE} {RTIME}

// Editor : sublime text{SUBLIME_VERSION}, tab size ({TABS})

// -----------------------------------------------------------------------------

- 你可以从设置中指定的文件中插入你自己的标题描述格式。

{YEAR}被替换为当前年份{DATE}被替换为创建日期{TIME}被替换为创建时间{RDATE}被替换为修订日期{RTIME}被替换为修订后的时间{FILE}被替换为文件名{TABS}被替换为标签大小{SUBLIME_VERSION}被替换为当前sublime text版本。

3. lnsert Snippet 插入片段 (ctrl+alt+p)

- 可以添加你的片段设置

{/* UI Configuration UI 配置 _________________________________________ */"context_menu": true,"verilog_ext": [ ".v", ".vh", ".sv", ".svh" ], // 表示context_menu"Generate Testbench": "show","Generate Testbench Ref/Imp": "hide","Module Wrapper": "hide","Simulation Template": "show","Insert Header": "show","Insert Snippet": "show","Instantiate Module": "show","Repeat Code with Numbers": "show","VCD to WaveDrom": "show",/* Core settings 核心设置 ____________________________________________ */// default prefix for a instance name 实例名称的默认前缀"inst_prefix": "inst_",// alignment (tab or space) 对齐方式(制表符或空格)"tab_assignment": false,"tab_port_declaration": true,"tab_signal_declaration": true,"tab_port_connection": false,/* Header / Snippet 标头/代码段 _________________________________________ */// header template file path 头模板文件路径"header": "example","auto_update_header": true,// parameterized snippets 参数化代码段"snippets" : {"Complex Multiplier" : { // example"codes" : "Packages/Verilog Gadget/template/verilog_cplxm.v","param" : ["AB", "BB"],"evals" : ["ZB=AB+BB+1"], // simple calculation only"descr" : "INPUTA , INPUTB [ complex mult ]","regex" : "\\s*(?P\\d+)\\s*[,.\\s]\\s*(?P\\d+)\\s*"// regex for parameter input},/* add more snippets here */},/* for Testbench ____________________________________________ */"reset" : [], // default asynchronous reset name, leave a blank not to use it 默认异步重置名称,留空不使用"sreset" : ["srstb"], // default synchronous reset name, leave a blank not to use it 默认同步重置名称,留空不使用它"clock" : ["clk", "uclk", "cclk"], // default clock name, leave a blank not to use it 默认时钟名称,留空不使用"wave_type" : "fsdb", // type of waveform, one of "fsdb", "vpd", "shm", "vcd" 波形类型"task_init" : true,"task_drive": true,

}

4. Instantiate Module 实例化模块

- 它解析了当前打开的文件的模块端口

- 它生成一个模块的实例文本

- 它复制生成的文本到剪贴板上

5. Simulation Template 仿真模板

6. Repeat Code with Numbers 用数字重复代码(ctrl+f12)

- 选择你想重复的代码,这可能包括Python的格式符号,如{…}。

- 在输入面板中输入一个范围,如下所示:[from]~[to],[↓step],[→step] 。

(例如0~10或0~10,2或10~0,-1或0~5,1,1...)。 - [↓step]表示行步,默认为1,[→step]表示列步,默认为0

- 代码以递增或递减的数字重复出现

- Python的格式符号支持变量格式:二进制,十六进制,前导零,…

- 要按原样使用’{‘,必须输入两次,如’{{'。

7. 代码自动对齐

选中想要对齐的代码,按下快捷键ctrl+shift+x

总结

以上就是本文要讲的内容。

上一篇:ES-搜索和查询

下一篇:零基础入门学习Python 04

相关内容

热门资讯

Linux-scheduler...

四、调度域 SDTL结构 linux内核使用SDTL结构体来组织CPU的层次关系 struct sc...

Retinanet网络与foc...

参考代码:https://github.com/yhenon/pytorch-reti...